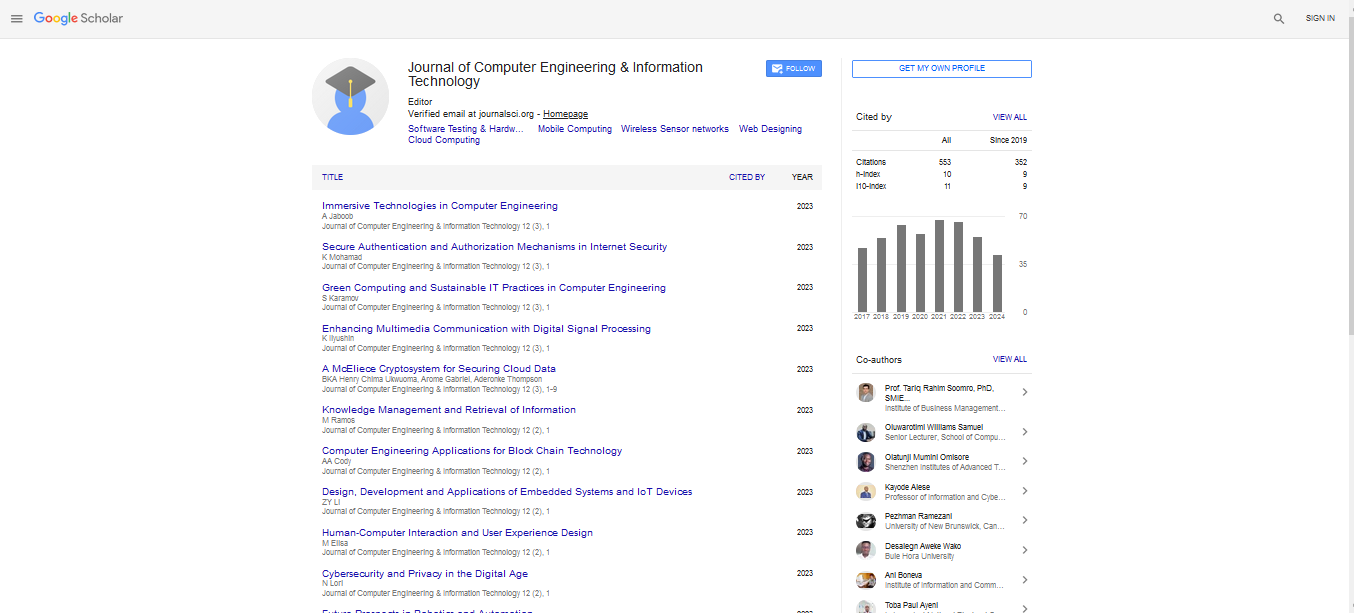

About the Journal of Computer Engineering & Information Technology

Journal of Computer Engineering & Information Technology (ISSN : 2324-9307) is a peer-reviewed scholarly journal and aims to publish the most complete and reliable source of information on the discoveries and current developments in the mode of original articles, review articles, case reports, short communications in all major themes pertaining to advances in computer engineering & information technology and making them available online freely without any restrictions or any other subscriptions to researchers worldwide.

Journal of Computer Engineering & Information Technology focuses on the topics that include:

- Computer Science

- Information Technology

- Software Testing & Hardware Technology

- Mobile Computing

- Wireless Sensor networks

- Web Designing

- Cloud Computing

- Big Data Analysis

- Visual Communication System

- Robotics

- Embedded systems

- E-Marketing

- Neural Networks, Artificial Intelligence

- VLSI design and testing

The Journal is using Editorial Tracking System for quality in review process. Editorial Tracking is an online manuscript submission, review and tracking system. Review processing is performed by the editorial board members of Journal of Computer Engineering & Information Technology or outside experts; at least two independent reviewers approval followed by editor approval is required for acceptance of any citable manuscript. Authors may submit manuscripts and track their progress through the online tracking system, hopefully to publication.

Submit Manuscript via Online Submission System

Confirmed Special Issues:

Current Trends in Applications for Software/Hardware Integration

2018 Journal Impact Factor is the ratio of the number of citations achieved in the year 2018 based on Google Search and Google Scholar Citations to the total number of articles published in the last two years i.e. in 2016 and 2017. Impact factor measures the quality of the Journal.

If ‘X’ is the total number of articles published in 2016 and 2017, and ‘Y’ is the number of times these articles were cited in indexed journals during 2016 then, impact factor = Y/X.

The Journal 5 year Impact Factor is 1.46* for the Year 2018.

Algorithms are the well organized series of steps for solving a particular problem with finite amount of space and time. Algorithms are generally used in Mathematical and computer sciences are created as functions.

Journals related to Algorithms

Algorithms, Journal of Algorithms, Journal of Discrete Algorithms, International Journal of Experimental Algorithms, ACM Transactions on Algorithms, Journal of Algorithms and Optimization, Journal of Algorithms & Computational Technology, Journal of Algorithms in Cognition Informatics and Logic.

Google Algorithms

You can send a new mail with this ; gmail.com login. This journal can be helpful for anything.

Artificial Intelligence

Artificial Intelligence is the developing arena of computer sciences wherein technology is advanced to make computers behave like Human Nervous system majorly brain. Artificial Intelligence has advanced in fields such as Computer games, Neural networks, Natural language, Expert Systems and Robotics.

Journals related to Artificial Intelligence

Artificial Intelligence, Journal of Artificial Intelligence Research, Synthesis Lectures on Artificial Intelligence and Machine Learning, Pattern Recognition, IEEE Transactions on Neural Networks and Learning Systems, Foundations and Trends in Machine Learning, IEEE Transactions on Pattern Analysis and Machine Intelligence, International Journal of Computer Vision, ACM Transactions on Intelligent Systems and Technology.

Big Data Analysis

Big Data Analysis is the science of examining large datasets consisting of different type of data to discover patterns, trends in market and other business information. Big Data assessment requires predictive analysis with extensive data mining.

Journals related to Big Data Analysis

Journal of Big Data, Big Data Research, International Journal of Big Data Intelligence, Open Journal of Big Data, International Journal of Big Data and Analytics in Healthcare, International Journal of Big Data, Big Data and Information Analytics, Big Data & Society.

Cloud Computing

Cloud Computing is a type of Internet based computing where different server’s storage and applications in an organization are delivered through internet. Cloud Computing helps in sharing the computational applications rather than having local servers and personal devices.

Journals related to Cloud Computing

Journal of Cloud Computing, International Journal of Cloud Applications and Computing, International Journal of Next-Generation Computing, International Journal of Cloud Computing and Services Science, Open Journal of Cloud Computing.

Computer graphics

Computer graphics is the Visual representation of data on computer screen can be termed as computer graphics. It is used for video games, advertising, movie making, scientific modelling etc. .

Journals related to Computer graphics

International Journal of Computer Graphics & Animation, Journal of Computer Graphics Techniques, International Journal of Computer Graphics, IEEE Computer Graphics and Applications, Computer Graphics and Image Processing, IEEE Transactions on Visualization and Computer Graphics, ACM Transactions on Graphics, Computers & Graphics .

Computer Science

Computer Science is the Research arena which includes fundamentals of computer, hardware, software and associated fields such as Electronics, Medical, Mathematics and Linguistics. In short Computer Science is the study of storage and transfer of information.

Journals related to Computer Science

Journal of Applied Bioinformatics & Computational Biology, Global Research in Computer Science, International Journal of Computer Science and Security, Computers and Education, Computers and Operations Research, Future Generation Computer Systems.

Data Management and Databases

Databases are the well organized entity of data. Data management system is the software package of computer technology structured for data defining, manipulating, retrieving and updating of data in Database.

Journals related to Data Management and Databases

International Journal of Database Management Systems, Journal of Database Management, Database Management & Information Retrieval, Journal of Information and Data Management.

Data Mining

Data Mining is exploring of knowledge regarding data from large data warehouses by computer assisted process. Data Mining tools help in future trends and behaviors with knowledge-driven decisions and work on existing software and hardware platforms to enhance the value of existing information resources and associated with new products and systems.

Journals related to Data Mining

Journal of Data Mining in Genomics & Proteomics, Journal of Informatics and Data Mining, International Journal of Biomedical Data Mining, International Journal of Sensor Networks and Data Communications, International Journal of Data Mining and Bioinformatics, International Journal of Knowledge Engineering and Data Mining, International Journal of Data Warehousing and Mining.

E-Marketing

E-Marketing is the online novel technology which uses internet and digital media facilities to avail goods and products for sale online. This E-Marketing technology helps in rapid traditional marketing, despite of size and type of business.

Journals related to E-Marketing

International Journal of Electronic Marketing and Retailing, International Journal of Internet Marketing and Advertising, International Journal of Online Marketing, Indian Journal of Marketing, International Journal of Marketing Studies, Journal of Global Marketing.

Embedded Systems

Embedded System is the area of computer science with the focus on larger mechanical or electrical system using real time computing constraints with the embedded association of hardware and mechanical parts.

Journals related to Embedded Systems

Electrical Engineering and Electronic Technology, Electrical & Electronic Systems, Biosensors & Bioelectronics, International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, Telecommunications System & Management, International Journal of Embedded Systems, EURASIP Journal on Embedded Systems, International Journal of Embedded Systems and Applications, Journal of Embedded Systems, International Journal of Embedded Systems, American Journal of Embedded Systems and Applications, International Journal of VLSI and Embedded Systems.

Information Technology

Information Technology, shortly IT is the Science of application of computer hardware, software, networking and distribution of data. Information Technology is rooted to fields of Telecommunication, Healthcare and Business Firms.

Journals related to Information Technology

Information Technology & Software Engineering, Information Technology & Software Engineering, IEEE Transactions on Information Theory, International Journal of Advancements in Technology, Research & Reviews: Journal of Engineering and Technology, Journal of the Association of Information Systems, Knowledge and Information Systems, Information Systems Research, Journal of Information Technology, Information Systems Journal.

Machine Learning is the part of artificial intelligence where the computers have ability to learn and changed to new data like human brains without any designed programming which have aspects like pattern recognition. Natural Language processing, the arena of Artificial intelligence deals with interaction of computers with human languages.

Journals related to Machine Learning & Natural Language Processing

ACM Transactions on Speech and Language Processing, Computational Linguistics, Computer Speech & Language, International Journal of Computational Linguistics and Applications, Transactions of the Association for Computational Linguistics, Machine Learning, Journal of Logic, Language and Information, Research on Language and Computation, Procesamiento del Lenguaje Natural Journal.

Mobile Computing

Mobile Computing is the advanced and developing computer application that allows voice and video transmission in the form of data through computer or wireless devices without any further linking. Mobile Computing in the breakthrough in the Computer Technology.

Journals related to Mobile Computing

IEEE Transactions on Mobile Computing, Pervasive and Mobile Computing, Mobile Networks and Applications, Mobile Computing and Communications Review, Wireless Communications and Mobile Computing, International Journal of Interactive Mobile Technologies.

Neural Networks

Neural Network/ Artificial Neural Network is the inspired version of biological Nervous system wherein large number of highly interconnected processing elements (neurons) working in unison to solve specific problems. ANN is configured for a specific application, such as pattern recognition or data classification, through a learning process.

Journals related to Neural Networks

Neural Networks Journal, Neural Networks, Neurocomputing, IEEE Transactions on Neural Networks, International Journal of Neural Systems, Neural Computing and Applications, Frontiers in Neurorobotics.

Robotics is the expertise and evolving field with areas covering Mechanical Engineering, Electrical Engineering and Computer Engineering. Robotics deals with the Ideas of defining, designing, construction, working and application of robots in different areas of technology.

Journals related to Robotics

Advances in Robotics & Automation, Biosensors & Bioelectronics, International Journal of Robotics Research, Journal of Field Robotics, IEEE Transactions on Robotics, IEEE Robotics and Automation Magazine, Autonomous Robots, Robotics and Autonomous Systems, Robotics and Computer-Integrated Manufacturing, Robotica, International Journal of Humanoid Robotics, Journal of Intelligent and Robotic Systems, Industrial Robot: An International Journal, Advanced Robotics, International Journal of Advanced Robotic Systems, International Journal of Robotics and Automation.

Software Testing & Hardware Technologies

Software Testing is the process of evaluating or validating the proper functioning of Software program defined by specific requirements. Hardware Technology is the science of exploring the physical components of Computer.

Journals related to Software Testing & Hardware Technology

Information Technology & Software Engineering, IEEE Transactions on Software Engineering, IEEE Software, ACM Transactions on Software Engineering and Methodology, Information and Software Technology, Automated Software Engineering, Software and Systems Modeling, Journal of Systems and Software.

Spam Regulation is the computer technology help in controlling the Spam, the unwanted and unsolicited mails into Inbox. Spam Regulation is maintained with specific Spam Act and is generally used in Corporate and IT Sectors.

Journals related to Spam Regulation

Journal of Cybersecurity, IEEE Security & Privacy, International Journal of Information Security, JISSec - Information Systems Security, Information and Computer Security, International Journal of Network Security, Cryptologia, International Journal of Cyber-Security and Digital Forensics, National Cybersecurity Institute Journal, International Journal of Information and Computer Security, Journal of Information Assurance & Cybersecurity.

Visual Communication System

Visual Communication is an art of presenting idea or data as an image, sign, poster, drawing, photography, advertisement or Animation. Visual communication commonly expressed with ASCII art, emoticon and embedded digital images.

Journals related to Visual Communication System

Journal of Visual Communication and Image Representation, Telecommunications System & Management, IEEE Transactions on Visualization and Computer Graphics, IEEE Transactions on Multimedia, Computer Vision and Image Understanding, Signal, Image and Video Processing, IEEE Transactions on Signal Processing, Visual Communications Journal, Journal of Visual Languages & Computing.

VLSI, the Very Large Scale Integration is defined as the method in which integrated circuit is formed by the union of thousands of transistors into a single silicon semiconductor microchip. The technology of VLSI design from its defining to testing is VLSI design and testing.

Journals related to VLSI Design and Testing

VLSI Design, Transactions on Very Large Scale Integration Systems, International journal of VLSI design & Communication Systems, Integration, The VLSI Journal, Journal of VLSI Design Tools & Technology, Journal of Advanced Research in Microelectronics and VLSI Design, Journal of Signal Processing Systems for Signal, Image, and Video Technology, Electrical Engineering and Electronic Technology, Electrical & Electronic Systems, Biosensors & Bioelectronics, International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, Telecommunications System & Management.

Web Designing

Web Designing is the art of designing the Website/WebPages from its creation with appropriate architecture, layout, content generation, graphic look and updating. Web Designing is based on Markup Language especially HTML (Hyper Text Markup Language).

Journals related to Web Designing

Advances in Robotics & Automation, Global Research in Computer Science, International Journal of Advancements in Technology, Information Technology & Software Engineering.

Wireless Sensor Networks

Wireless Sensor Networks are the advanced gateway technology with the spatially distributed systems called sensors to assess the physical and environmental conditions without any backend connectivity to the wires and distributed nodes. Each wireless network can scale from tens to hundreds of nodes and seamlessly integrate with existing wired measurement and control systems.

Journals related to Wireless Sensor Networks

IEEE Transactions on Wireless Communications, Wireless Networks, Wireless Personal Communications, IEEE Wireless Communications, KICS Journal of Communications and Networks, Wireless Communications and Mobile Computing.

Fast Editorial Execution and Review Process (FEE-Review Process):

Journal of Computer Engineering & Information Technology is participating in the Fast Editorial Execution and Review Process (FEE-Review Process) with an additional prepayment of $99 apart from the regular article processing fee. Fast Editorial Execution and Review Process is a special service for the article that enables it to get a faster response in the pre-review stage from the handling editor as well as a review from the reviewer. An author can get a faster response of pre-review maximum in 3 days since submission, and a review process by the reviewer maximum in 5 days, followed by revision/publication in 2 days. If the article gets notified for revision by the handling editor, then it will take another 5 days for external review by the previous reviewer or alternative reviewer.

Acceptance of manuscripts is driven entirely by handling editorial team considerations and independent peer-review, ensuring the highest standards are maintained no matter the route to regular peer-reviewed publication or a fast editorial review process. The handling editor and the article contributor are responsible for adhering to scientific standards. The article FEE-Review process of $99 will not be refunded even if the article is rejected or withdrawn for publication.

The corresponding author or institution/organization is responsible for making the manuscript FEE-Review Process payment. The additional FEE-Review Process payment covers the fast review processing and quick editorial decisions, and regular article publication covers the preparation in various formats for online publication, securing full-text inclusion in a number of permanent archives like HTML, XML, and PDF, and feeding to different indexing agencies.

Spanish

Spanish  Chinese

Chinese  Russian

Russian  German

German  French

French  Japanese

Japanese  Portuguese

Portuguese  Hindi

Hindi